Ziel des Gesamtprojektes

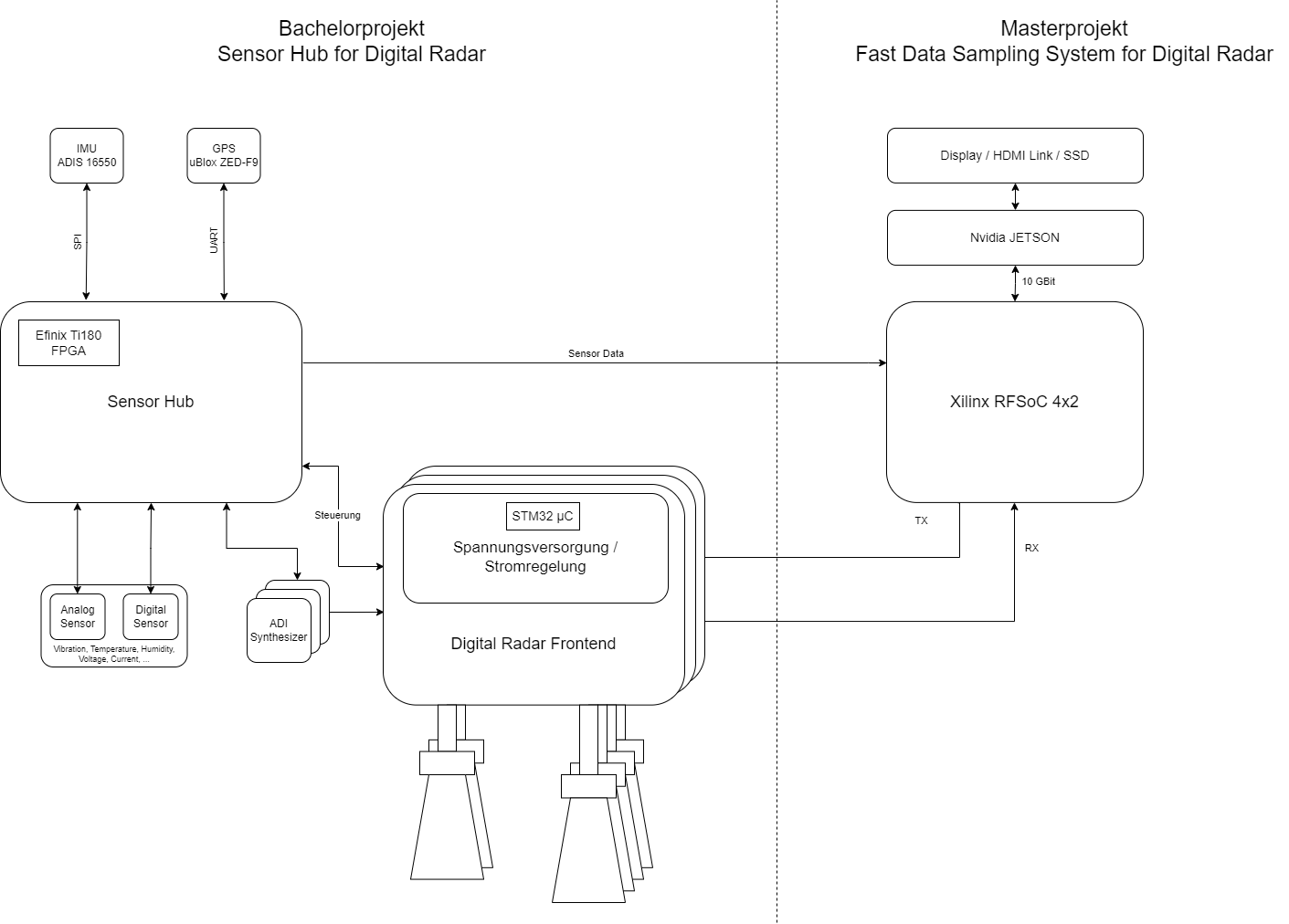

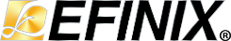

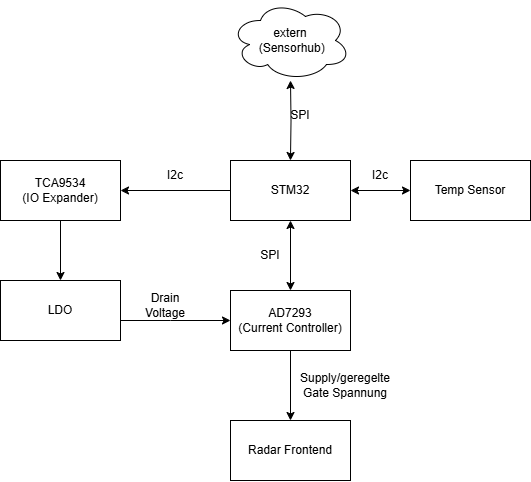

Das Gesamtprojekt hat das Ziel, eine topographische Vermessung mittels Radar und Drohnen zu ermöglichen. Ein Schwerpunkt ist die Nutzung von Synthetic Aperture Radar (SAR) Bildern, die eine präzise Analyse und Abbildung ermöglichen. Zusätzlich werden Sensor- und Radardaten synchronisiert, um eine nahtlose Integration zu gewährleisten. Durch Monitoring und Fehlerbehandlung von Sensoren wird die Zuverlässigkeit gesteigert, während Steuerungsmöglichkeiten für Radarfrontends eine flexible Anpassung an unterschiedliche Szenarien ermöglichen.

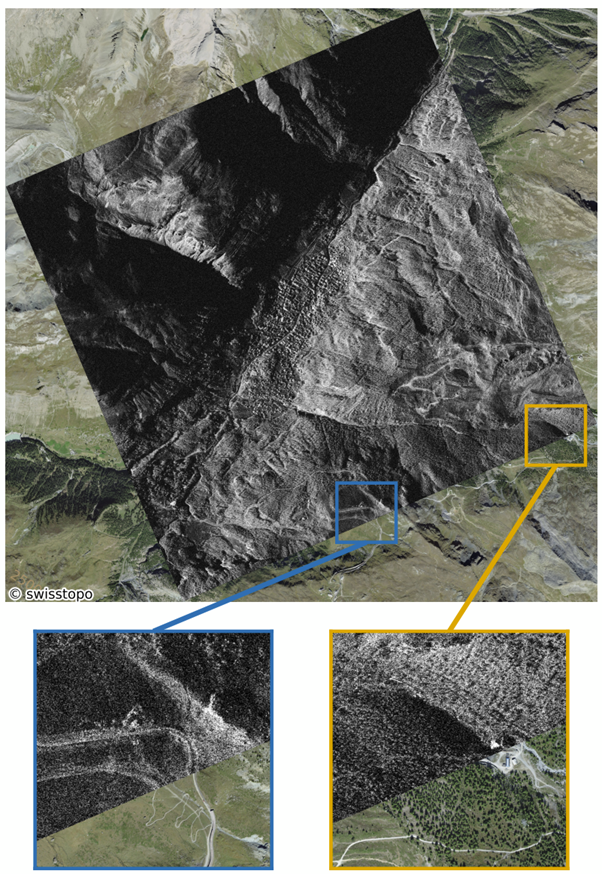

SAR-Bilder

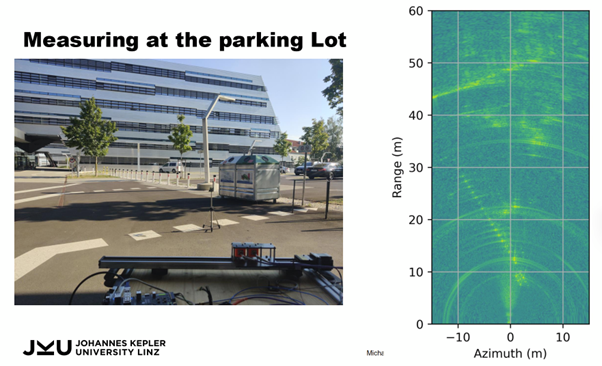

In Abbildung 1 sieht man ein Beispiel eines SAR-Bildes. SAR-Bilder sind eine spezielle Form von Radaraufnahmen, die eine hohe räumliche Auflösung bieten. Sie werden durch die Bewegung des Radarsensors und die Verarbeitung der empfangenen Signale erzeugt. SAR-Bilder sind besonders nützlich für topographische Vermessungen, da sie eine detaillierte Darstellung der Oberfläche ermöglichen. Durch die Kombination von SAR-Bildern mit anderen Sensordaten können präzise 3D-Modelle erstellt werden, die für eine Vielzahl von Anwendungen nützlich sind.

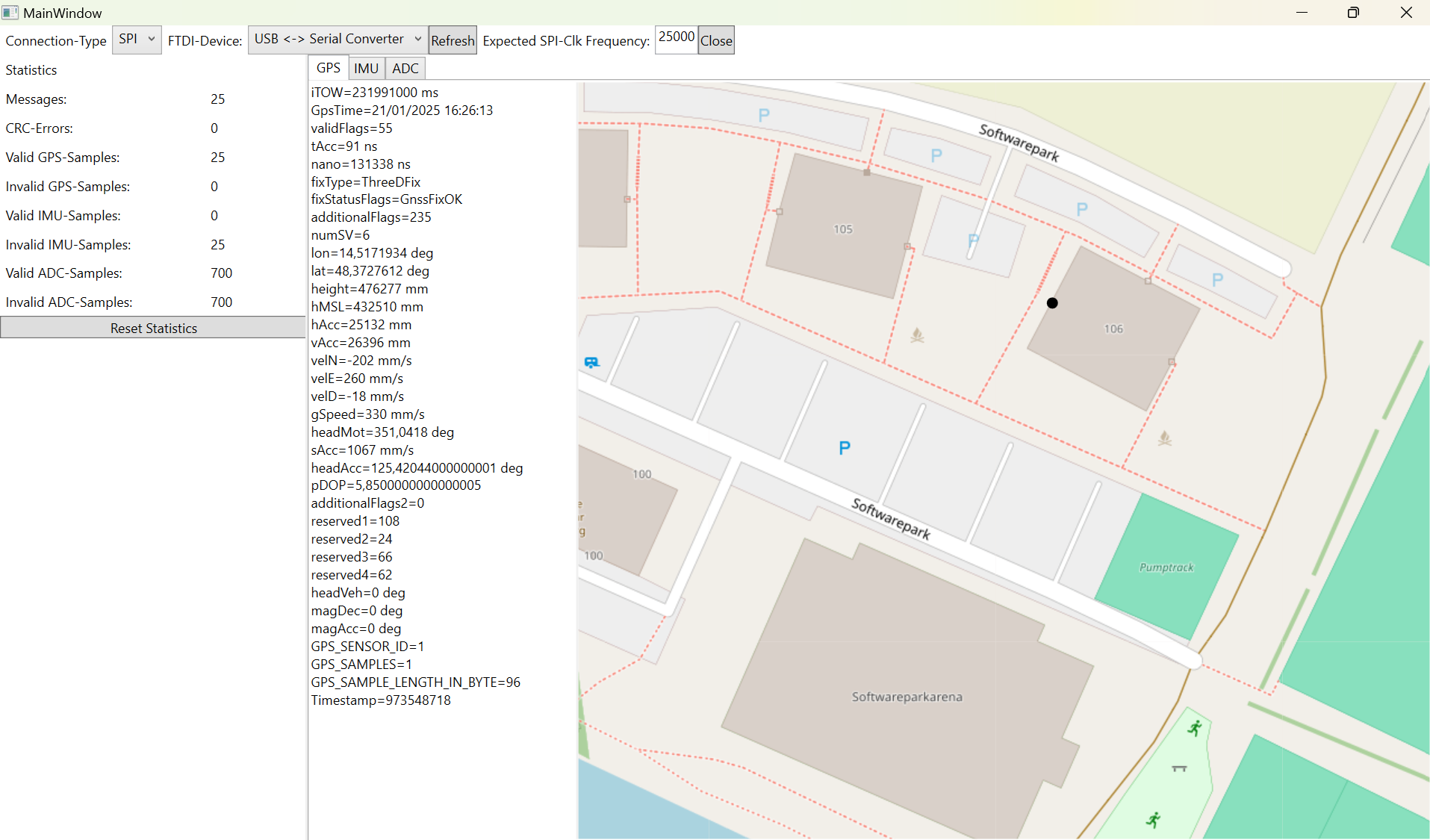

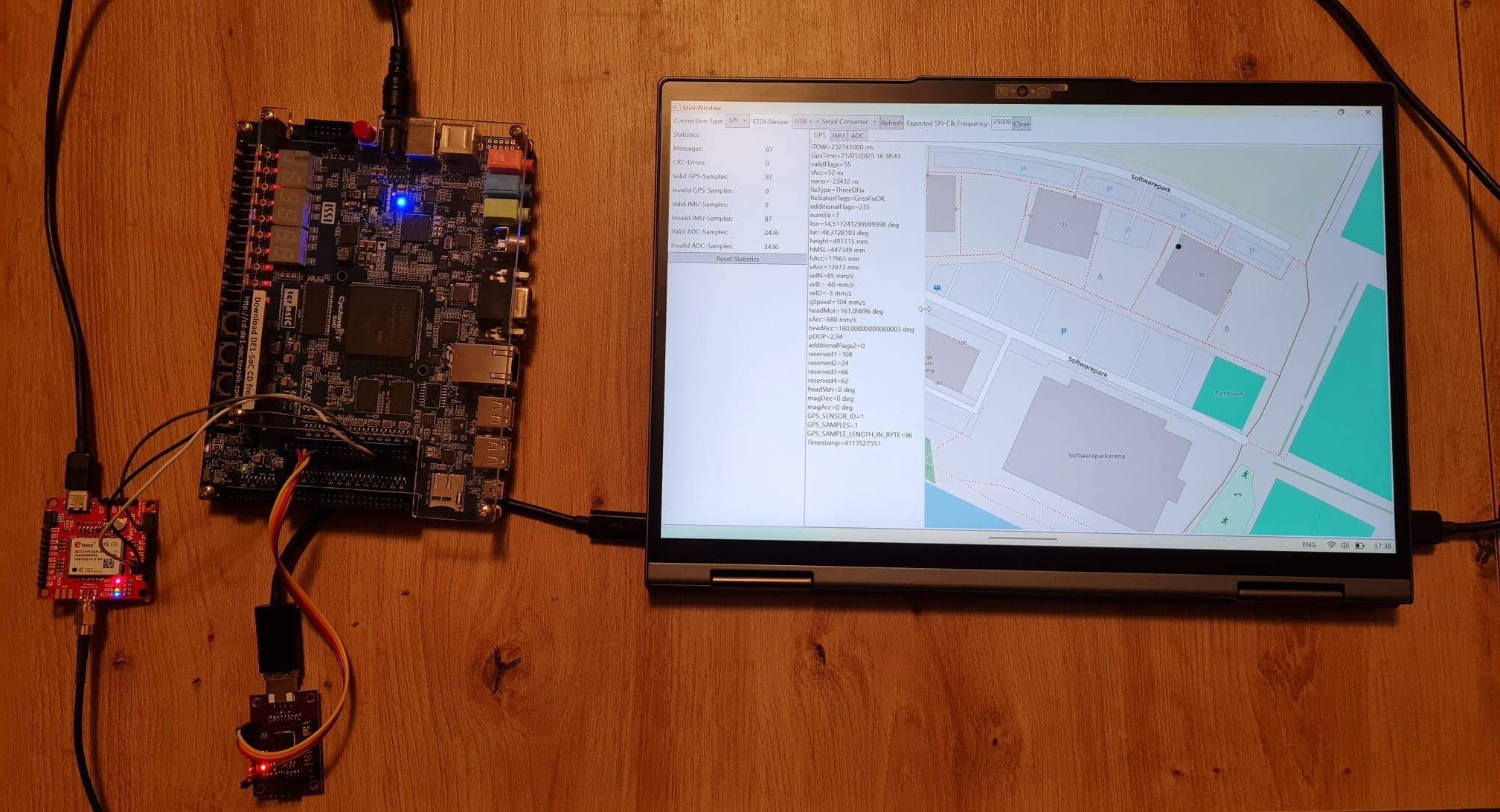

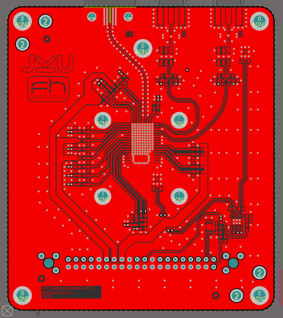

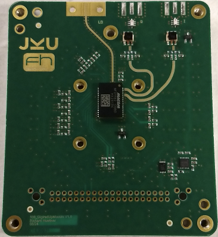

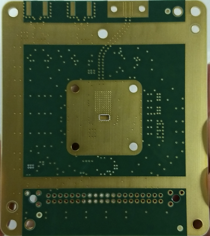

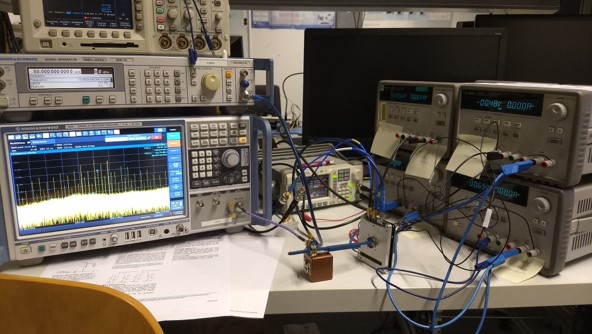

Messungen mit Radarfrontend am JKU Parkplatz

Die Master-Projektgruppe hat bereits Messungen mit dem Radarfrontend am JKU Parkplatz erfolgreich durchgeführt. Aus diesen Messungen und unseren Sensordaten, kann dann ein SAR-Bild erstellt werden.